|            |          |       |         |            |                 | REVISIONS  |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|------------|----------|-------|---------|------------|-----------------|------------|---------------------------|-----------|------|-------|----------------------------------------------------|-----------------------|-------------|----------------------|-----------------------|----------------------|-----------------------|------------------------|--------|-------|-----|

|            |          |       |         | Ľ          | TR              |            |                           |           | DESC | RIPTI | ION DATE                                           |                       |             |                      |                       | APPROVED             |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

| Prenared   | in acc   | ordan | co witi | h ASME Y1  | 11 21           |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      | \/م                   | ndor it                | em dra | awina |     |

| riopulou   | in doo   | oraan | 00 111  |            | 1.21            |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      | vo                    |                        | onnan  | umig  |     |

| REV        |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

| PAGE       |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

| REV        |          |       |         |            |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

| PAGE       | 18       | 19    | 20      | 21 22      | 23              |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

| REV STA    |          |       | REV     | ,          |                 |            |                           |           |      |       |                                                    |                       |             |                      |                       |                      |                       |                        |        |       |     |

| OF PAGE    | ES       |       | PAG     | Ε          | 1               | 2          | 3                         | 4         | 5    | 6     | 7                                                  | 8                     | 9           | 10                   | 11                    | 12                   | 13                    | 14                     | 15     | 16    | 17  |

| PMIC N/A   | 4        |       |         | PREPAR     | ED BY           | ,          |                           |           |      |       | DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                       |             |                      |                       |                      |                       |                        |        |       |     |

|            |          |       | F       | Phu H.     | Nguy            | en         | Phu H. Nguyen             |           |      |       |                                                    |                       |             |                      |                       |                      | .mil/                 |                        |        |       |     |

| Original d | late of  | drawi |         | CHECKED BY |                 |            |                           |           |      | http  | )://ww                                             | w.lane                | Janun       |                      | ie.dia                |                      |                       |                        |        |       |     |

| Ŷ          | YMM      | טט    | ng      | CHECKE     | D BY            |            |                           |           |      |       | TIT                                                | LE                    | <u>http</u> | <u>)://ww</u>        | w.land                | Janun                |                       | <u>ie.uia</u>          |        |       |     |

| 1          | 13-01-17 |       |         | CHECKE     |                 | Phu H.     | Nguy                      | en        |      |       | MIC                                                | ROC                   |             | JIT,                 | LINE                  | AR,                  | 1.2 0                 | SHz (                  |        |       |     |

|            |          |       | ng      | CHECKE     | F               |            | Nguy                      | en        |      |       | MIC<br>DIS                                         |                       |             | JIT,<br>DN IC        | LINE<br>;, 1.6        | AR,<br>6 GHz         | 1.2 C<br>z INP        | GHz (<br>UTS,          |        |       | RS, |

|            |          | 17    | ng      |            | F<br>ED BY      | ,          | Nguy                      |           |      |       | MIC<br>DIS                                         |                       |             | JIT,<br>DN IC        | LINE<br>;, 1.6        | AR,<br>6 GHz         | 1.2 0                 | GHz (<br>UTS,          |        |       | RS, |

|            |          | 17    | ng      |            | F<br>ED BY<br>T | ,<br>homas |                           | ess       |      |       | MIC<br>DIS<br>FIV                                  |                       |             | JIT,<br>DN IC        | LINE<br>;, 1.6        | AR,<br>6 GHz         | 1.2 C<br>z INP        | GHz (<br>UTS,          |        |       | ΧS, |

|            |          | 17    | ng      | APPROV     | F<br>ED BY<br>T | ,<br>homas | s M. He<br>E <b>NT. N</b> | ess       |      |       | MIC<br>DIS<br>FIV                                  | CROC<br>STRIE<br>E OL |             | JIT,<br>DN IC<br>TS, | LINE<br>C, 1.6<br>MON | AR,<br>6 GH2<br>OLIT | 1.2 C<br>z INP        | GHz (<br>UTS,<br>SILIC |        |       | S,  |

|            |          | 17    | ng      | APPROV     | F<br>ED BY<br>T | ,<br>homas | s M. He<br>E <b>NT. N</b> | ess<br>O. |      |       | MIC<br>DIS<br>FIV                                  | CROC<br>STRIE<br>E OL |             | JIT,<br>DN IC<br>TS, | LINE<br>C, 1.6<br>MON | AR,<br>6 GH2<br>OLIT | 1.2 (<br>z INP<br>HIC | GHz (<br>UTS,<br>SILIC |        |       | S,  |

### 1. SCOPE

1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance 1.2 GHz clock distribution IC, 1.6 GHz inputs, dividers, five outputs microcircuit, with an operating temperature range of -55°C to +85°C.

1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| V62/12656<br>Drawing<br>number | - <u>01</u><br>Device type<br>(See 1.2.1) | Case outline<br>(See 1.2.2) | E<br>Lead finish<br>(See 1.2.3)            |

|--------------------------------|-------------------------------------------|-----------------------------|--------------------------------------------|

| 1.2.1 Device type(s).          |                                           |                             |                                            |

| Device type                    | <u>Generic</u>                            | <u>Circu</u>                | it function                                |

| 01                             | AD9512-EP                                 | 1.2 GHz clock distribution  | IC, 1.6 GHz inputs, dividers, five outputs |

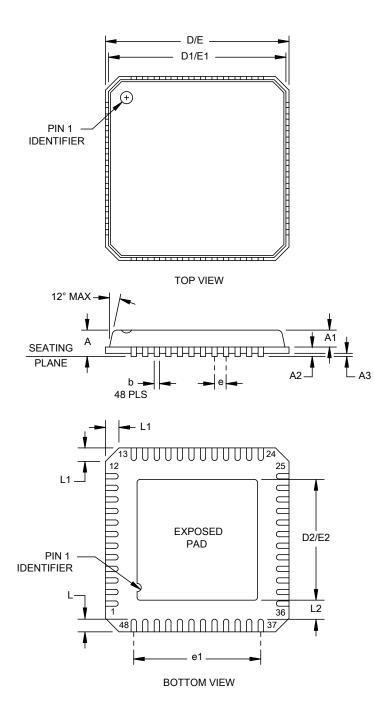

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95        | Package style                 |

|----------------|----------------|---------------------|-------------------------------|

| х              | 48             | JEDEC MO-220-VKKD-2 | Lead Frame Chip Scale Package |

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator          | <u>Material</u>                                                                              |  |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|

| A<br>B<br>C<br>D<br>E<br>Z | Hot solder dip<br>Tin-lead plate<br>Gold plate<br>Palladium<br>Gold flash palladium<br>Other |  |  |  |  |

|                            |                                                                                              |  |  |  |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12656</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV            | PAGE 2                   |

#### 1.3 Absolute maximum ratings. 1/

| VS with respect to GND                           | -0.3 V to +3.6 V                 |

|--------------------------------------------------|----------------------------------|

| DSYNC/DSYNCB with respect to GND                 |                                  |

| RSET with respect to GND                         | -0.3 V to V <sub>S</sub> + 0.3 V |

| CLK1, CLK1B, CLK2, CLK2B with respect to GND     | -0.3 V to V <sub>S</sub> + 0.3 V |

| CLK1 with respect to CLK1B                       | -1.2 V to +1.2 V                 |

| CLK2 with respect to CLK2B                       | -1.2 V to +1.2 V                 |

| SCLK, SDIO, SDO, CSB with respect to GND         | -0.3 V to V <sub>S</sub> + 0.3 V |

| OUT0, OUT1, OUT2, OUT3, OUT4 with respect to GND | -0.3 V to V <sub>S</sub> + 0.3 V |

| FUNCTION with respect to GND                     | -0.3 V to V <sub>S</sub> + 0.3 V |

| SYNC STATUS with respect to GND                  | -0.3 V to V <sub>S</sub> + 0.3 V |

| Storage temperature range                        | -65°C to 150°C                   |

| Junction temperature                             | 150°C                            |

| Lead temperature (10 sec)                        | 300°C                            |

#### 1.4 Thermal characteristics.

Thermal resistance 2/

| Case outline | θ <sub>JA</sub> | Unit |

|--------------|-----------------|------|

| Case X       | 28.5            | °C/W |

### 2. APPLICABLE DOCUMENTS

#### JEDEC – SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEP95 – Registered and Standard Outlines for Semiconductor Devices

JESD51-7 - High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

(Copies of these documents are available online at http://www.jedec.org or from JEDEC – Solid State Technology Association, 3103 North 10th Street, Suite 240–S, Arlington, VA 22201.)

#### 3. REQUIREMENTS

3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12656</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV            | PAGE 3                   |

<sup>&</sup>lt;u>1</u>/ Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

<sup>2/</sup> Thermal impedance measurements were taken on a 4-layer board in still air, in accordance with EIA/JESD51-7.

3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 <u>Design, construction, and physical dimension</u>. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

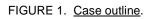

- 3.5.3 <u>Terminal function</u>. The terminal function shall be as shown in figure 3.

- 3.5.4 <u>Functional block diagram</u>. The functional block diagram shall be as shown in figure 4.

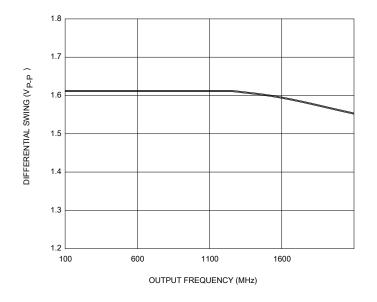

- 3.5.5 <u>LVPECL differential output swing vs frequency</u>. The LVPECL differential output swing vs frequency shall be as shown in figure 5.

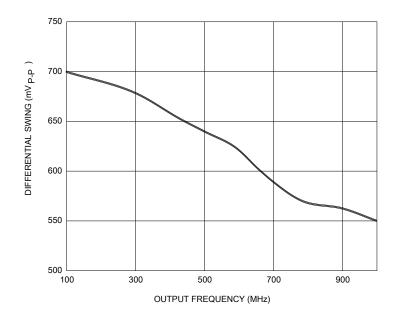

- 3.5.6 <u>LVDS differential output swing vs frequency</u>. The LVDS differential output swing vs frequency shall be as shown in figure 6.

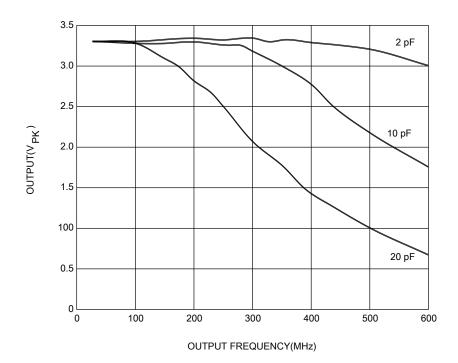

- 3.5.7 <u>CMOS single ended output swing vs frequency and load</u>. The CMOS single ended output swing vs frequency and load shall be as shown in figure 7.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |  |

|-----------------------|------|----------------|-----------|--|

| COLUMBUS, OHIO        | A    | 16236          | V62/12656 |  |

|                       |      | REV            | PAGE 4    |  |

|  | TABLE I. | Electrical | performance | characteristics. | 1/ |

|--|----------|------------|-------------|------------------|----|

|--|----------|------------|-------------|------------------|----|

| Test                            | Symbol           | Symbol Test conditions <u>2/</u>                   |                       | Limits             |                       |        |  |

|---------------------------------|------------------|----------------------------------------------------|-----------------------|--------------------|-----------------------|--------|--|

|                                 |                  |                                                    |                       | Min Typ            |                       |        |  |

|                                 |                  | CLOCK INPUTS                                       |                       |                    |                       |        |  |

| Clock inputs (CLK1, CLK2) 3/    | 1                | 1                                                  | 1                     | 1                  | r                     | 1      |  |

| Input frequency                 |                  |                                                    | 0                     |                    | 1.6                   | GHz    |  |

| Input sensitivity               |                  | <u>4</u> /                                         |                       | 150 <u>7</u> /     |                       | mV p-p |  |

| Input level                     |                  | <u>5</u> /                                         |                       |                    | 2 <u>8</u> /          | V р-р  |  |

| Input common mode voltage       | V <sub>CM</sub>  | <u>6</u> /                                         | 1.45                  | 1.6                | 1.7                   | V      |  |

| input common mode venage        | • Civi           | At -40°C to +85°C                                  | 1.5                   | 1.6                | 1.7                   | V      |  |

| Input common mode range         | V <sub>CMR</sub> | With 200 mV p-p signal applied, dc-coupled         | 1.3                   |                    | 1.8                   | V      |  |

| Input sensitivity, single ended |                  | CLK2 ac-coupled; CLK2B ac bypassed to<br>RF ground |                       | 150                |                       | mV p-p |  |

| Input resistance                |                  | Self-biased                                        | 4.0                   | 4.8                | 5.6                   | kΩ     |  |

| Input capacitance               |                  |                                                    |                       | 2                  |                       | pF     |  |

|                                 |                  | CLOCK OUTPUTS                                      |                       |                    |                       |        |  |

| LVPECL clock outputs (Termina   | tion = 50 Ω      | 2 to V <sub>S</sub> – 2 V)                         |                       | -                  |                       |        |  |

| OUT0, OUT1, OUT2; Differential  |                  | Output level 0x3D (0x3E) (0x3F)[3:2] = 10b         |                       |                    |                       |        |  |

| Output frequency                |                  | See FIGURE 5                                       |                       |                    | 1200                  | MHz    |  |

| Output high voltage             | Vон              |                                                    | V <sub>S</sub> – 1.22 | $V_{\rm S} - 0.98$ | $V_{\rm S}-0.93$      | V      |  |

| Output low voltage              | Vol              |                                                    | $V_{S} - 2.10$        | $V_{S} - 1.80$     | V <sub>S</sub> – 1.67 | V      |  |

| Output differential voltage     | Vod              |                                                    | 660                   | 810                | 965                   | mV     |  |

| LVDS clock outputs (Termination | n = 100 Ω c      | differential; default)                             | 1                     | 1                  | r                     | 1      |  |

| OUT3, OUT4; Differential        |                  | Output level 0x40 (0x41)[2:1] = 01b                |                       |                    |                       |        |  |

|                                 |                  | 3.5 mA termination current                         |                       |                    |                       |        |  |

| Output frequency                |                  | See FIGURE 6                                       |                       |                    | 800                   | MHz    |  |

| Differential output voltage     | V <sub>OD</sub>  |                                                    | 250                   | 360                | 450                   | mV     |  |

| Delta V <sub>OD</sub>           |                  |                                                    |                       |                    | 25                    | mV     |  |

| Output offset voltage           | Vos              | At full temperature range                          | 1.05                  | 1.23               | 1.375                 | V      |  |

|                                 |                  | At -40°C to +85°C                                  | 1.125                 | 1.23               | 1.375                 | V      |  |

| Delta V <sub>OS</sub>           |                  |                                                    |                       |                    | 25                    | mV     |  |

| Short Circuit current           | $I_{SA}, I_{SB}$ | Output shorted to GND                              |                       | 14                 | 24                    | mA     |  |

| CMOS clock outputs              | 1                |                                                    | •                     |                    |                       | •      |  |

| OUT3, OUT4                      |                  | Single ended measurements;                         |                       |                    |                       |        |  |

|                                 |                  | B outputs: inverted, termination open              |                       |                    |                       |        |  |

| Output frequency                |                  | With 5 pF load each outputs, see FIGURE 7          |                       |                    | 250                   | MHz    |  |

| Output voltage high             | V <sub>OH</sub>  | @ 1 mA load                                        | $V_{S}-0.1$           |                    |                       | V      |  |

| Output voltage low              | Vol              | @ 1 mA load                                        |                       |                    | 0.1                   | V      |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12656</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV            | PAGE 5                   |

| Test                                                                  | Symbol              | Test conditions                          |        | Limits |      | Unit     |

|-----------------------------------------------------------------------|---------------------|------------------------------------------|--------|--------|------|----------|

|                                                                       |                     | <u>2</u> /                               | Min    | Тур    | Max  |          |

|                                                                       | TIMIN               | G CHARACTERISTICS                        |        |        |      |          |

| <b>LVPECL</b> (Termination = 50 $\Omega$ to V <sub>S</sub> – 2V, Outp | out level 0x3       | D (0x3E)(0x3F)[3:2] =10b)                |        |        |      |          |

| Output rise time                                                      | t <sub>RP</sub>     | 20% to 80%, measured differentially      |        | 130    | 180  | ps       |

| Output fall time                                                      | t <sub>FP</sub>     | 80% to 20%, measured differentially      |        | 130    | 180  |          |

| Propagation delay, t <sub>PELC</sub> , CLK-TO-LVPECL                  | DUT <u>9</u> /      |                                          |        |        |      |          |

| Divide = Bypass                                                       |                     | At full temperature range                | 320    | 490    | 635  | ps       |

| Bindo - Bypado                                                        |                     | At -40°C to +85°C                        | 335    | 490    | 635  |          |

| Divide = $2$ to $32$                                                  |                     | At full temperature range                | 360    | 545    | 695  | 1        |

|                                                                       |                     | At -40°C to +85°C                        | 375    | 545    | 695  | 1        |

| Variation with temperature                                            |                     |                                          |        | 0.5    |      | ps/°C    |

| Output skew, LVPECL outputs                                           |                     | •                                        |        |        |      | <u>.</u> |

| OUT1 to OUT0 on same part <u>10</u> /                                 | t <sub>SKP</sub>    |                                          | 70     | 100    | 140  | ps       |

| OUT1 to OUT2 on same part <u>10</u> /                                 | t <sub>SKP</sub>    |                                          | 15     | 45     | 80   | 1        |

| OUT0 to OUT2 on same part <u>10</u> /                                 | t <sub>SKP</sub>    |                                          | 45     | 65     | 90   | 1        |

| All LVPECL OUT across multiple parts <u>11</u> /                      | t <sub>SKP_AB</sub> |                                          |        |        | 275  | 1        |

| Same LVPECL OUT across multiple parts 11/                             | t <sub>SKP_AB</sub> |                                          |        |        | 130  |          |

| <b>LVDS</b> (Termination = $100 \Omega$ differential, Output          | t level 0x40        | (0x41)[2:1] = 01b, 3.5 mA termination cu | rrent) |        |      |          |

| Output rise time                                                      | t <sub>RL</sub>     | 20% to 80%, measured differentially      |        | 200    | 350  | ps       |

| Output fall time                                                      | t <sub>FL</sub>     | 80% to 20%, measured differentially      |        | 210    | 350  | 1        |

| Propagation delay, t <sub>LVDS</sub> , CLK-to-LVDS OUT                | <u>9</u> /          |                                          |        |        |      |          |

| OUT3 to OUT4                                                          |                     |                                          |        |        | -    | -        |

| Divide = Bypass                                                       |                     | At full temperature range                | 0.97   | 1.33   | 1.59 | ns       |

|                                                                       |                     | At -40°C to +85°C                        | 0.99   | 1.33   | 1.59 |          |

| Divide = $2$ to $32$                                                  |                     | At full temperature range                | 1.02   | 1.38   | 1.64 |          |

|                                                                       |                     | At -40°C to +85°C                        | 1.04   | 1.38   | 1.64 |          |

| Variation with temperature                                            |                     |                                          |        | 0.9    |      | ps/°C    |

| Output skew, LVDS outputs                                             |                     |                                          |        |        |      |          |

| OUT3 to OUT4 on same part, <u>10</u> /                                | t <sub>SKV</sub>    |                                          | -85    |        | +270 | ps       |

| All LVDS OUTs across multiple parts <u>11</u> /                       | t <sub>SKV_AB</sub> |                                          |        |        | 450  |          |

| Same LVDS OUT across multiple parts <u>11</u> /                       | t <sub>SKV_AB</sub> |                                          |        |        | 325  |          |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/12656 |

|                       |      | REV            | PAGE 6    |

| Test                                                   | Symbol              | Test conditions                       |      | Limits |      | Unit  |

|--------------------------------------------------------|---------------------|---------------------------------------|------|--------|------|-------|

|                                                        | <u>2</u> /          |                                       | Min  | Тур    | Max  |       |

| I                                                      | IMING CHA           | ARACTERISTICS-Continued.              |      |        |      |       |

| CMOS (B outputs are inverted; termination = op         | en)                 |                                       |      |        |      |       |

| Output rise time                                       | t <sub>RC</sub>     | 20% to 80%, $C_{LOAD} = 3 \text{ pF}$ |      | 681    | 865  | ps    |

| Output fall time                                       | t <sub>FC</sub>     | 80% to 20%, $C_{LOAD} = 3 \text{ pF}$ |      | 646    | 992  |       |

| Propagation delay, t <sub>CMOS</sub> , CLK to CMOS OUT | <u>9</u> /          |                                       |      |        |      |       |

| Divide = Bypass                                        |                     | At full temperature range             | 1.0  | 1.39   | 1.71 | ns    |

| Divide - Dypade                                        |                     | At -40°C to +85°C                     | 1.02 | 1.39   | 1.71 |       |

| Divide = $2$ to $32$                                   |                     | At full temperature range             | 1.05 | 1.44   | 1.76 |       |

| Divide - 2 10 32                                       |                     | At -40°C to +85°C                     | 1.07 | 1.44   | 1.76 |       |

| Variation with temperature                             |                     |                                       |      | 1      |      | ps/°C |

| Output skew, CMOS outputs                              | •                   |                                       |      |        |      | •     |

| OUT3 to OUT4 on same part, <u>10</u> /                 | t <sub>sĸc</sub>    |                                       | -140 | +145   | +300 | ps    |

| All CMOS OUT across multiple parts <u>11</u> /         | t <sub>SKC_AB</sub> |                                       |      |        | 650  |       |

| Same CMOS OUT across multiple parts <u>11</u> /        | t <sub>SKC_AB</sub> |                                       |      |        | 500  |       |

| LVPECL to LVDS OUT (Everything the same;               | different log       | ic type LVPECL to LVDS on same part)  |      |        |      |       |

| Output skew                                            | t <sub>SKP_V</sub>  |                                       | 0.73 | 0.92   | 1.14 | ns    |

| LVPECL to CMOS OUT (Everything the same;               | different log       | gic type LVPECL to CMOS on same part) |      |        |      |       |

| Output skew                                            | t <sub>SKP_C</sub>  |                                       | 0.87 | 1.14   | 1.43 | ns    |

| LVDS to CMOS OUT (Everything the same; dif             | ferent logic        | type LVDS to CMOS on same part)       |      |        |      |       |

| Output skew                                            | t <sub>skv c</sub>  |                                       | 158  | 353    | 506  | ps    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/12656 |

|                       | REV  |                | PAGE 7    |

| Test                                    | Symbol | Test conditions          |     | Limits |     | Unit  |

|-----------------------------------------|--------|--------------------------|-----|--------|-----|-------|

|                                         |        | <u>2</u> /               | Min | Тур    | Max |       |

|                                         | CLOCK  | OUTPUT PHASE NOISE       |     |        |     |       |

| CLK1 to LVPECL and additive phase noise |        |                          |     |        |     |       |

| CLK1 = 622.08 MHz, OUT = 622.08 MHz     |        | Input slew rate > 1 V/ns |     |        |     |       |

| Divide Ratio = 1                        |        |                          |     |        |     |       |

| @ 10 Hz Offset                          |        |                          |     | -125   |     | dBc/H |

| @ 100 Hz Offset                         |        |                          |     | -132   |     |       |

| @ 1 kHz Offset                          |        |                          |     | -140   |     |       |

| @ 10 KHz Offset                         |        |                          |     | -148   |     |       |

| @100 kHz Offset                         |        |                          |     | -153   |     |       |

| > 1 MHz Offset                          |        |                          |     | -154   |     |       |

| CLK1 = 622.08 MHz, OUT = 155.52 MHz     |        |                          |     |        |     |       |

| Divide Ratio = 4                        |        |                          |     |        |     |       |

| @ 10 Hz Offset                          |        |                          |     | -128   |     | dBc/H |

| @ 100 Hz Offset                         |        |                          |     | -140   |     |       |

| @ 1 kHz Offset                          |        |                          |     | -148   |     |       |

| @ 10 KHz Offset                         |        |                          |     | -155   |     |       |

| @100 kHz Offset                         |        |                          |     | -161   |     |       |

| > 1 MHz Offset                          |        |                          |     | -161   |     |       |

| CLK1 = 622.08 MHz, OUT = 38.88 MHz      |        |                          |     |        |     |       |

| Divide Ratio = 16                       |        |                          |     |        |     |       |

| @ 10 Hz Offset                          |        |                          |     | -135   |     | dBc/H |

| @ 100 Hz Offset                         |        |                          |     | -145   |     |       |

| @ 1 kHz Offset                          |        |                          |     | -158   |     |       |

| @ 10 KHz Offset                         |        |                          |     | -165   |     |       |

| @100 kHz Offset                         |        |                          |     | -165   |     |       |

| > 1 MHz Offset                          |        |                          |     | -166   |     |       |

| CLK1 = 491.52 MHz, OUT = 61.44 MHz      |        |                          |     |        |     |       |

| Divide Ratio = 8                        |        |                          |     |        |     |       |

| @ 10 Hz Offset                          |        |                          |     | -131   |     | dBc/H |

| @ 100 Hz Offset                         |        |                          |     | -142   |     |       |

| @ 1 kHz Offset                          |        |                          |     | -153   |     |       |

| @ 10 KHz Offset                         |        |                          |     | -160   |     |       |

| @100 kHz Offset                         |        |                          |     | -165   |     |       |

| > 1 MHz Offset                          |        |                          |     | -165   |     |       |

| CLK1 = 491.52 MHz, OUT = 245.76 MHz     |        |                          |     | 1      |     | 1     |

| Divide Ratio = 2                        |        |                          |     |        |     |       |

| @ 10 Hz Offset                          |        |                          |     | -125   |     | dBc/H |

| @ 100 Hz Offset                         |        |                          |     | -132   |     |       |

| @ 1 kHz Offset                          |        |                          |     | -140   |     |       |

| @ 10 KHz Offset                         |        |                          |     | -151   |     |       |

| @100 kHz Offset                         |        |                          |     | -157   |     |       |

| > 1 MHz Offset                          |        |                          |     | -158   |     |       |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/12656 |

|                       |      | REV            | PAGE 8    |

| Test                                    | Symbol         | Test conditions         |  | Limits |     | Unit   |

|-----------------------------------------|----------------|-------------------------|--|--------|-----|--------|

|                                         |                | <u>2</u> /              |  | Тур    | Max |        |

|                                         | CLOCK OUTPUT   | PHASE NOISE- Continued. |  |        |     |        |

| CLK1 to LVPECL and additive phase noise | e – Continued. |                         |  |        |     |        |

| CLK1 = 245.76 MHz, OUT = 61.44 MHz      |                |                         |  |        |     |        |

| Divide Ratio = 4                        |                |                         |  |        |     |        |

| @ 10 Hz Offset                          |                |                         |  | -138   |     | dBC/Hz |

| @ 100 Hz Offset                         |                |                         |  | -144   |     |        |

| @ 1 kHz Offset                          |                |                         |  | -154   |     |        |

| @ 10 KHz Offset                         |                |                         |  | -163   |     |        |

| @100 kHz Offset                         |                |                         |  | -164   |     |        |

| > 1 MHz Offset                          |                |                         |  | -165   |     |        |

| CLK1 to LVDS additive phase noise       |                |                         |  |        |     |        |

| CLK1 = 622.08 MHz, OUT = 622.08 MHz     |                |                         |  |        |     |        |

| Divide Ratio = 1                        |                |                         |  |        |     |        |

| @ 10 Hz Offset                          |                |                         |  | -100   |     | dBC/Hz |

| @ 100 Hz Offset                         |                |                         |  | -110   |     |        |

| @ 1 kHz Offset                          |                |                         |  | -118   |     |        |

| @ 10 KHz Offset                         |                |                         |  | -129   |     |        |

| @100 kHz Offset                         |                |                         |  | -135   |     |        |

| @1 MHz Offset                           |                |                         |  | -140   |     |        |

| > 10 MHz Offset                         |                |                         |  | -148   |     |        |

| CLK1 = 622.08 MHz, OUT = 155.52 MHz     |                |                         |  |        |     |        |

| Divide Ratio = 4                        |                |                         |  |        |     |        |

| @ 10 Hz Offset                          |                |                         |  | -112   |     | dBC/H  |

| @ 100 Hz Offset                         |                |                         |  | -122   |     |        |

| @ 1 kHz Offset                          |                |                         |  | -132   |     |        |

| @ 10 KHz Offset                         |                |                         |  | -142   |     |        |

| @100 kHz Offset                         |                |                         |  | -148   |     |        |

| @1 MHz Offset                           |                |                         |  | -152   |     |        |

| > 10 MHz Offset                         |                |                         |  | -155   |     |        |

| CLK1 = 491.52 MHz, OUT = 245.76 MHz     |                |                         |  |        |     |        |

| Divide Ratio = 2                        |                |                         |  |        |     |        |

| @ 10 Hz Offset                          |                |                         |  | -108   |     | dBC/H  |

| @ 100 Hz Offset                         |                |                         |  | -118   |     |        |

| @ 1 kHz Offset                          |                |                         |  | -128   |     |        |

| @ 10 KHz Offset                         |                |                         |  | -138   |     |        |

| @100 kHz Offset                         |                |                         |  | -145   |     |        |

| @1 MHz Offset                           |                |                         |  | -148   |     |        |

| > 10 MHz Offset                         |                |                         |  | -154   |     |        |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/12656 |

|                       |      | REV            | PAGE 9    |

| Test                                    | Symbol         | Test conditions         |  | Limits |     | Unit   |

|-----------------------------------------|----------------|-------------------------|--|--------|-----|--------|

|                                         |                | <u>2</u> /              |  | Тур    | Max |        |

|                                         | CLOCK OUTPUT P | PHASE NOISE- Continued. |  |        |     |        |

| CLK1 to LVDS additive phase noise - Con | tinued.        |                         |  |        |     |        |

| CLK1 = 491.52 MHz, OUT = 122.88 MHz     |                |                         |  |        |     |        |

| Divide Ratio = 4                        |                |                         |  |        |     |        |

| @ 10 Hz Offset                          |                |                         |  | -118   |     | dBC/Hz |

| @ 100 Hz Offset                         |                |                         |  | -129   |     |        |

| @ 1 kHz Offset                          |                |                         |  | -136   |     |        |

| @ 10 KHz Offset                         |                |                         |  | -147   |     |        |

| @100 kHz Offset                         |                |                         |  | -153   |     |        |

| @1 MHz Offset                           |                |                         |  | -156   |     |        |

| > 10 MHz Offset                         |                |                         |  | -158   |     |        |

| CLK1 = 245.76 MHz, OUT = 245.76 MHz     |                |                         |  |        |     |        |

| Divide Ratio = 1                        |                |                         |  |        |     |        |

| @ 10 Hz Offset                          |                |                         |  | -108   |     | dBC/Hz |

| @ 100 Hz Offset                         |                |                         |  | -118   |     |        |

| @ 1 kHz Offset                          |                |                         |  | -128   |     |        |

| @ 10 KHz Offset                         |                |                         |  | -138   |     |        |

| @100 kHz Offset                         |                |                         |  | -145   |     |        |

| @1 MHz Offset                           |                |                         |  | -148   |     |        |

| > 10 MHz Offset                         |                |                         |  | -155   |     |        |

| CLK1 = 245.76 MHz, OUT = 122.88 MHz     |                |                         |  |        |     |        |

| Divide Ratio = 2                        |                |                         |  |        |     |        |

| @ 10 Hz Offset                          |                |                         |  | -118   |     | dBC/Hz |

| @ 100 Hz Offset                         |                |                         |  | -127   |     |        |

| @ 1 kHz Offset                          |                |                         |  | -137   |     |        |

| @ 10 KHz Offset                         |                |                         |  | -147   |     |        |

| @100 kHz Offset                         |                |                         |  | -154   |     |        |

| @1 MHz Offset                           |                |                         |  | -156   |     |        |

| > 10 MHz Offset                         |                |                         |  | -158   |     |        |

| DLA LAND AND MARITIME | SIZE CODE IDENT NO. |     | DWG NO.          |

|-----------------------|---------------------|-----|------------------|

| COLUMBUS, OHIO        | A 16236             |     | <b>V62/12656</b> |

|                       |                     | REV | PAGE 10          |

| Test                                  | Symbol      | Test conditions         |  | Limits |     |        |

|---------------------------------------|-------------|-------------------------|--|--------|-----|--------|

|                                       |             | <u>2</u> /              |  | Тур    | Max |        |

| C                                     | LOCK OUTPUT | PHASE NOISE- Continued. |  |        |     |        |

| CLK1 to CMOS additive phase noise     |             |                         |  |        |     |        |

| CLK1 = 245.76 MHz, OUT = 245.76 MHz   |             |                         |  |        |     |        |

| Divide Ratio = 1                      |             |                         |  |        |     |        |

| @ 10 Hz Offset                        |             |                         |  | -110   |     | dBC/Hz |

| @ 100 Hz Offset                       |             |                         |  | -121   |     |        |

| @ 1 kHz Offset                        |             |                         |  | -130   |     |        |

| @ 10 KHz Offset                       |             |                         |  | -140   |     |        |

| @100 kHz Offset                       |             |                         |  | -145   |     |        |

| @1 MHz Offset                         |             |                         |  | -149   |     |        |

| > 10 MHz Offset                       |             |                         |  | -156   |     |        |

| CLK1 = 245.76 MHz, OUT = 61.44 MHz    |             |                         |  |        |     |        |

| Divide Ratio = 4                      |             |                         |  |        |     |        |

| @ 10 Hz Offset                        |             |                         |  | -122   |     | dBC/Hz |

| @ 100 Hz Offset                       |             |                         |  | -132   |     |        |

| @ 1 kHz Offset                        |             |                         |  | -143   |     |        |

| @ 10 KHz Offset                       |             |                         |  | -152   |     |        |

| @100 kHz Offset                       |             |                         |  | -158   |     |        |

| @1 MHz Offset                         |             |                         |  | -160   |     |        |

| > 10 MHz Offset                       |             |                         |  | -162   |     |        |

| CLK1 = 78.6432 MHz, OUT = 78.6432 MHz |             |                         |  |        |     |        |

| Divide Ratio = 1                      |             |                         |  |        |     |        |

| @ 10 Hz Offset                        |             |                         |  | -122   |     | dBC/Hz |

| @ 100 Hz Offset                       |             |                         |  | -132   |     |        |

| @ 1 kHz Offset                        |             |                         |  | -140   |     |        |

| @ 10 KHz Offset                       |             |                         |  | -150   |     |        |

| @100 kHz Offset                       |             |                         |  | -155   |     |        |

| @1 MHz Offset                         |             |                         |  | -158   |     |        |

| > 10 MHz Offset                       |             |                         |  | -160   |     |        |

| CLK1 = 78.6432 MHz, OUT = 39.3216 MHz |             |                         |  |        |     |        |

| Divide Ratio = 2                      |             |                         |  |        |     |        |

| @ 10 Hz Offset                        |             |                         |  | -128   |     | dBC/H  |

| @ 100 Hz Offset                       |             |                         |  | -136   |     |        |

| @ 1 kHz Offset                        |             |                         |  | -146   |     |        |

| @ 10 KHz Offset                       |             |                         |  | -155   |     |        |

| @100 kHz Offset                       |             |                         |  | -161   |     |        |

| > 1 MHz Offset                        |             |                         |  | -162   |     |        |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/12656 |

|                       |      | REV            | PAGE 11   |

| Test                                           | Test conditions                                        |     | Limits |     | Unit   |

|------------------------------------------------|--------------------------------------------------------|-----|--------|-----|--------|

|                                                | <u>2</u> /                                             | Min | Тур    | Max |        |

| CLOCK OU                                       | TPUT PHASE NOISE- Continued.                           |     |        |     |        |

| LVPECL output additive time jitter             |                                                        |     |        |     |        |

| CLK1 = 622.08 MHz                              |                                                        |     | 40     |     | fs rms |

| Any LVPECL (OUT0 to OUT2) = 622.08 MHz,        | BW = 12 kHz to 20 MHz (OC-12)                          |     |        |     |        |

| Divide ratio = 1                               |                                                        |     |        |     |        |

| CLK1 = 622.08 MHz                              |                                                        |     | 55     |     | fs rms |

| Any LVPECL (OUT0 to OUT2) = 155.52 MHz,        | BW = 12 kHz to 20 MHz (OC-3)                           |     |        |     |        |

| Divide ratio = 4                               |                                                        |     |        |     |        |

| CLK1 = 400 MHz                                 | Calculated from SNR of ADC method;                     |     | 215    |     | fs rms |

|                                                | fc = 100 MHz with $A_{IN}$ = 170 MHz                   |     |        |     |        |

| Any LVPECL (OUT0 to OUT2) = 100 MHz,           |                                                        |     |        |     |        |

| Divide ratio = 4                               |                                                        |     |        |     |        |

| CLK1 = 400 MHz                                 | Calculated from SNR of ADC method;                     |     | 215    |     | fs rms |

|                                                | fc = 100 MHz with $A_{IN}$ = 170 MHz                   |     |        |     |        |

| Any LVPECL (OUT0 to OUT2) = 100 MHz,           |                                                        |     |        |     |        |

| Divide ratio = 4                               |                                                        |     |        |     |        |

| Other LVPECL = 100 MHz                         | Interferer(s)                                          |     |        |     |        |

| Both LVDS (OUT3, OUT4) = 100 MHz               | Interferer(s)                                          |     |        |     |        |

| CLK1 = 400 MHz                                 | Calculated from SNR of ADC method;                     |     | 222    |     | fs rms |

|                                                | $fc = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$ |     |        |     |        |

| Any LVPECL (OUT0 to OUT2) = 100 MHz,           |                                                        |     |        |     |        |

| Divide ratio = $4$                             |                                                        |     |        |     |        |

| Other LVPECL = 50 MHz                          | Interferer(s)                                          |     |        |     |        |

| Both LVDS (OUT3, OUT4) = 50 MHz                | Interferer(s)                                          |     |        |     |        |

| CLK1 = 400 MHz                                 | Calculated from SNR of ADC method;                     |     | 225    |     | fs rms |

|                                                | $fc = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$ |     |        |     |        |

| Any LVPECL (OUT0 to OUT2) = 100 MHz,           |                                                        |     |        |     |        |

| Divide ratio = $4$                             |                                                        |     |        |     |        |

| Other LVPECL = 50 MHz                          | Interferer(s)                                          |     |        |     |        |

| Both CMOS (OUT3, OUT4) = 50 MHz (B outputs Off |                                                        |     |        |     |        |

| CLK1 = 400 MHz                                 | Calculated from SNR of ADC method;                     |     | 225    |     | fs rms |

|                                                | $fc = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$ |     |        |     |        |

| Any LVPECL (OUT0 to OUT2) = 100 MHz,           |                                                        |     |        |     |        |

| Divide ratio = 4                               |                                                        |     |        |     |        |

| Other LVPECL = 50 MHz                          | Interferer(s)                                          |     |        |     |        |

| Both CMOS (OUT3, OUT4) = 50 MHz (B outputs On  | ) Interferer(s)                                        |     |        |     |        |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12656</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV            | PAGE 12                  |

| Test                                 | Test conditions                                        |     | Limits |     | Unit   |

|--------------------------------------|--------------------------------------------------------|-----|--------|-----|--------|

|                                      | <u>2</u> /                                             | Min | Тур    | Max |        |

| CLOCK                                | OUTPUT PHASE NOISE- Continued.                         |     |        |     |        |

| LVDS output additive time jitter     |                                                        |     |        |     |        |

| CLK1 = 400 MHz                       | Calculated from SNR of ADC method;                     |     | 264    |     | fs rms |

|                                      | $fc = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$ |     |        |     |        |

| LVDS (OUT3) = 100 MHz                |                                                        |     |        |     |        |

| Divide ratio = 4                     |                                                        |     |        |     |        |

| CLK1 = 400 MHz                       | Calculated from SNR of ADC method;                     |     | 319    |     | fs rms |

|                                      | $fc = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$ |     |        |     |        |

| LVDS (OUT4) = 100 MHz                |                                                        |     |        |     |        |

| Divide ratio = 4                     |                                                        |     |        |     |        |

| CLK1 = 400 MHz                       | Calculated from SNR of ADC method;                     |     | 395    |     | fs rms |

|                                      | $fc = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$ |     |        |     |        |

| LVDS (OUT3) = 100 MHz                |                                                        |     |        |     |        |

| Divide ratio = 4                     |                                                        |     |        |     |        |

| LVDS (OUT4) = 50 MHz                 | Interferer(s)                                          |     |        |     |        |

| All LVPECL = 50 MHz                  | Interferer(s)                                          |     |        |     |        |

| CLK1 = 400 MHz                       | Calculated from SNR of ADC method;                     |     | 395    |     | fs rms |

|                                      | $fc = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$ |     |        |     |        |

| LVDS (OUT4) = 100 MHz                |                                                        |     |        |     |        |

| Divide ratio = 4                     |                                                        |     |        |     |        |

| LVDS (OUT3) = 50 MHz                 | Interferer(s)                                          |     |        |     |        |

| All LVPECL = 50 MHz                  | Interferer(s)                                          |     |        |     |        |

| CLK1 = 400 MHz                       | Calculated from SNR of ADC method;                     |     | 367    |     | fs rms |

|                                      | fc = 100 MHz with $A_{IN}$ = 170 MHz                   |     |        |     |        |

| LVDS (OUT3) = 100 MHz                |                                                        |     |        |     |        |

| Divide ratio = 4                     |                                                        |     |        |     |        |

| CMOS (OUT4) = 50 MHz (B Outputs Off) | Interferer(s)                                          |     |        |     |        |

| All LVPECL = 50 MHz                  | Interferer(s)                                          |     |        |     |        |

| CLK1 = 400 MHz                       | Calculated from SNR of ADC method;                     |     | 367    |     | fs rms |

|                                      | fc = 100 MHz with $A_{IN}$ = 170 MHz                   |     |        |     |        |

| LVDS (OUT4) = 100 MHz                |                                                        |     |        |     |        |

| Divide ratio = 4                     |                                                        |     |        |     |        |

| CMOS (OUT3) = 50 MHz (B Outputs Off) | Interferer(s)                                          |     |        |     |        |

| All LVPECL = 50 MHz                  | Interferer(s)                                          |     |        |     |        |

| CLK1 = 400 MHz                       | Calculated from SNR of ADC method;                     |     | 548    |     | fs rms |

|                                      | fc = 100 MHz with $A_{IN}$ = 170 MHz                   |     |        |     |        |

| LVDS (OUT3) = 100 MHz                |                                                        |     |        |     |        |

| Divide ratio = 4                     |                                                        |     |        |     |        |

| CMOS (OUT4) = 50 MHz (B Outputs On)  | Interferer(s)                                          |     |        |     |        |

| All LVPECL = 50 MHz                  | Interferer(s)                                          |     |        |     |        |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/12656 |

|                       |      | REV            | PAGE 13   |

| Test                                           | Test conditions                                        |     | Limits |     |        |  |

|------------------------------------------------|--------------------------------------------------------|-----|--------|-----|--------|--|

|                                                | <u>2</u> /                                             | Min | Тур    | Max |        |  |

| CLOCK OUTP                                     | UT PHASE NOISE- Continued.                             |     |        |     |        |  |

| LVDS output additive time jitter – Continued.  |                                                        |     |        |     |        |  |

| CLK1 = 400 MHz                                 | Calculated from SNR of ADC method;                     |     | 548    |     | fs rms |  |

|                                                | $fc = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$ |     |        |     |        |  |

| LVDS (OUT4) = 100 MHz                          |                                                        |     |        |     |        |  |

| Divide ratio = 4                               |                                                        |     |        |     |        |  |

| CMOS (OUT3) = 50 MHz (B Outputs On)            | Interferer(s)                                          |     |        |     |        |  |

| All LVPECL = 50 MHz                            | Interferer(s)                                          |     |        |     |        |  |

| CMOS output additive time jitter               |                                                        |     |        |     |        |  |

| CLK1 = 400 MHz                                 | Calculated from SNR of ADC method;                     |     | 275    |     |        |  |

|                                                | fc = 100 MHz with $A_{IN}$ = 170 MHz                   |     |        |     |        |  |

| Both CMOS (OUT3, OUT4) = 100 MHz (B output On) |                                                        |     |        |     |        |  |

| Divide ratio = 4                               |                                                        |     |        |     |        |  |

| CLK1 = 400  MHz                                | Calculated from SNR of ADC method;                     |     | 400    |     |        |  |

|                                                | $fc = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$ |     |        |     |        |  |

| CMOS (OUT3) = 100 MHz (B output On)            |                                                        |     |        |     |        |  |

| Divide ratio = 4                               |                                                        |     |        |     |        |  |

| AII LVPECL = 50 MHz                            | Interferer(s)                                          |     |        |     |        |  |

| LVDS (OUT4) = 50 MHz                           | Interferer(s)                                          |     |        |     |        |  |

| CLK1 = 400 MHz                                 | Calculated from SNR of ADC method;                     |     | 374    |     |        |  |

|                                                | $fc = 100 \text{ MHz}$ with $A_{IN} = 170 \text{ MHz}$ |     |        |     |        |  |

| CMOS (OUT3) = 100 MHz (B output On)            |                                                        |     |        |     |        |  |

| Divide ratio = 4                               |                                                        |     |        |     |        |  |

| All LVPECL = 50 MHz                            | Interferer(s)                                          |     |        |     |        |  |

| CMOS (OUT4) = 50 MHz (B output Off)            | Interferer(s)                                          |     |        |     |        |  |

| CLK1 = 400  MHz                                | Calculated from SNR of ADC method;                     |     | 555    |     |        |  |

|                                                | $fc = 100 MHz$ with $A_{IN} = 170 MHz$                 |     |        |     |        |  |

| CMOS (OUT3) = 100 MHz (B output On)            |                                                        |     |        |     |        |  |

| Divide ratio = 4                               |                                                        |     |        |     |        |  |

| All LVPECL = 50 MHz $(D \text{ subsub } O^2)$  | Interferer(s)                                          |     |        |     |        |  |

| CMOS (OUT4) = 50 MHz (B output On)             | Interferer(s)                                          |     |        | 1   | L      |  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12656</b> |

|                       |      | REV            | PAGE 14          |

| Test                                    | Symbol             | Test conditions    |     | Limits |     | Unit                     |

|-----------------------------------------|--------------------|--------------------|-----|--------|-----|--------------------------|

|                                         |                    | <u>2</u> /         | Min | Тур    | Max | 1                        |

|                                         | S                  | ERIAL CONTROL PORT |     |        |     |                          |

| CSB, SCLK (Inputs) <u>12</u> /          |                    |                    | r   |        |     |                          |

| Input logic 1 voltage                   |                    |                    | 2.0 |        |     | V                        |

| Input logic 0 voltage                   |                    |                    |     |        | 0.8 |                          |

| Input logic 1 current                   |                    |                    |     | 110    |     | μA                       |

| Input logic 0 current                   |                    |                    |     |        | 1   |                          |

| Input capacitance                       |                    |                    |     | 2      |     | pF                       |

| SDIO (when input)                       |                    |                    |     |        | _   |                          |

| Input logic 1 voltage                   |                    |                    | 2.0 |        |     | V                        |

| Input logic 0 voltage                   |                    |                    |     |        | 0.8 |                          |

| Input logic 1 current                   |                    |                    |     | 10     |     | nA                       |

| Input logic 0 current                   |                    |                    |     | 10     |     |                          |

| Input capacitance                       |                    |                    |     | 2      |     | pF                       |

| SDIO, SDO (Outputs)                     |                    |                    |     |        |     |                          |

| Input logic 1 voltage                   |                    |                    | 2.7 |        |     | V                        |

| Input logic 0 voltage                   |                    |                    |     |        | 0.4 |                          |

| Timing                                  |                    |                    |     |        |     |                          |

| Clock rate (SCLK, 1/t <sub>SCLK</sub> ) |                    |                    |     |        | 25  | MHz                      |

| Pulse width high                        | t <sub>PWH</sub>   |                    | 16  |        |     | ns                       |